AMD Llano A8-3850 APU - Lynx Plattform im Test (3/15)

AMD Llano APU: Bis zu vier x86 Kerne

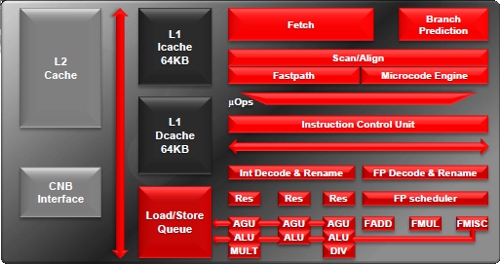

Die "Stars" genannten x86 Kerne der "Llano" APU-Familie sind im Grunde alte Bekannte. Sie stammen von den "Deneb"-Kernen ab, die in AMDs Phenom II ihr Werk verrichten. AMD hat sie jedoch noch einmal überarbeitet, wie sich an einigen Punkten zeigt.

So verfügen die Kerne nun in einigen Modellen über die Turbo CORE Technik, wie sie erstmals in den Phenom II X6 Prozessoren zur Anwendung kamen. Außerdem verfügen die APUs vergleichsweise über keinen L3 Cache mehr, wodurch im Grunde genommen die größte Ähnlichkeit zu den Athlon II CPUs besteht.

Als, wenn man so will, "Ausgleich" verfügen die vierkernigen A8- und A6-Series APUs über 1 MB L2 Cache pro Kern, das ist doppelt so viel wie bei den Quadcores der Phenom II- und Athlon II-Serien. Insgesamt verspricht sich AMD durch den vergrößerten L2 Cache und weitere Optimierungen eine Erhöhung der Intructions per Cycle (IPC) um etwa sechs Prozent.

Mit Sicherheit wird der Wegfall eines L3 Caches auch zum Teil über die schnelle Anbindung des Systemspeichers kompensiert, worauf wir im Verlauf des Artikels noch einmal gesondert eingehen werden.

Für Sparsamkeit und dadurch auch geringe Abwärme soll dabei ein neuer Fertigungsprozess sorgen: 32 nm Strukturbreite in der Silicon on Insultaor Technologie mit High-k Metal Gates. Damit zieht AMD dem großen Rivalen Intel nach, der seine CPUs schon längst in 32 nm fertigt und noch viel länger High-k Metal Gates einsetzt.

Dazu gesellt sich bei einigen Modellen die Turbo CORE Technologie. Hierbei steht der APU ein Gesamtbudget an TDP zur Verfügung, welches sie dynamisch ausreizen darf. Wie bei der PowerTUNE Technik der High-End GPUs von AMD wird über die gesamte APU hinweg digital die Auslastung gemessen und somit der Energieverbrauch berechnet. Wenn die Grafikeinheit nicht ihr gesamtes Energiebudget ausreizt, so dürfen die x86 Kerne unter Berücksichtigung der TDP-Grenze den Turbo zünden, was dann mehr Takt bedeutet.

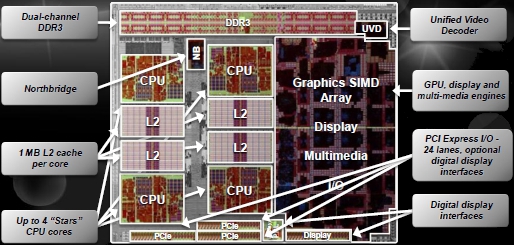

Wie das Die-Foto von AMD zeigt, befinden sich die x86 Kerne eingerahmt von DDR3-Controller einerseits und PCI Express Schnitstellen andererseits im Chip und nehmen in etwa so viel Platz ein wie die Radeon HD Grafikeinheit. Neben den üblichen Stromsparmechanismen und Low-Power-States kann die APU auch einzelne Teileinheiten per Power-Gating von der Energiezufuhr trennen oder diese verminden. Dazu zählen die x86 Kerne insgesamt (Package C6 State), die Radeon HD Grafik mit Shadern und UVD 3 Einheit und zusätzlich wird die Energiezufuhr für die Northbridge dynamisch in Abhängigkeit diverser Paramter angepasst (NB P-States, GPU Power States, PCI Express Geschwindigkeit, Arbeitsbelastung des UVD 3). Einzelne x86 Kerne können die Llano APUs elektrisch jedoch nicht gezielt abschalten - an dieser Stelle besteht also noch etwas Verbesserungspotential für die nächste APU-Generation.

Making Memory for Memory Makers

Making Memory for Memory Makers  Making Memory for Memory Makers

Making Memory for Memory Makers  Making Memory for Memory Makers

Making Memory for Memory Makers  Making Memory for Memory Makers

Making Memory for Memory Makers