AMD Athlon 600 MHz AMD Athlon 600 MHz

|

Hardware/CPUs |

|

|

|

The next Generation

Der Athlon Prozessor ist ein Prozessor der

siebten Generation und dem PIII daher auch eine Generation voraus. Ganze 22 Millionen

Transitoren verrichten im Athlon ihre Arbeit. Zum Vergleich, beim PIII sind es gerade mal

9,5 Millionen. Auf dem Bild unten kann man sehr sch�n den schematischen Aufbau der CPU

sehen. In dem Prozessor k�nnen bis zu 9 Funktionseinheiten (rot) parallel arbeiten. Da

sind zum einen drei Integer Einheiten (Integer Execution Unit, IEU) und die drei

Adressberechnungseinheiten (Adress Generetion Unit, AGU) sowie auf der anderen Seite die 3

Einheiten der FPU mit Namen FSTORE, FADD und FMUL.

Damit der Athlon Prozessor seine drei IEUs auch richtig ausnutzen kann, ist

der Instruction Decoder in der Lage pro Takt drei x86-Befehle zu dekodieren. Dekodieren

bedeutet dabei, da� der Prozessor die x86-Befehle in sogenannte ROPs umwandelt. ROPs sind

einfache, RISC �hnlich Befehle, die der Prozessor direkt verarbeiten kann, also sozusagen

"Befehlsatome". Ein vierter Decoder wandelt zus�tzlich komplexe Befehle �ber

ein Microcode ROM in mehere ROPs um. Die ROPs werden dann in der Instruction Control Unit

zwischengespeichert bevor sie verarbeitet werden, wobei bis zu 72 St�ck in der

Instruction Control Unit zwischengelagert werden. Damit der Athlon Prozessor seine drei IEUs auch richtig ausnutzen kann, ist

der Instruction Decoder in der Lage pro Takt drei x86-Befehle zu dekodieren. Dekodieren

bedeutet dabei, da� der Prozessor die x86-Befehle in sogenannte ROPs umwandelt. ROPs sind

einfache, RISC �hnlich Befehle, die der Prozessor direkt verarbeiten kann, also sozusagen

"Befehlsatome". Ein vierter Decoder wandelt zus�tzlich komplexe Befehle �ber

ein Microcode ROM in mehere ROPs um. Die ROPs werden dann in der Instruction Control Unit

zwischengespeichert bevor sie verarbeitet werden, wobei bis zu 72 St�ck in der

Instruction Control Unit zwischengelagert werden.

Im Pentium III l�uft das prinzipiell genauso

ab, dieser verf�gt aber nur �ber zwei parallel arbeitende Decoder. Der dritte Decoder

ist, wie beim Athlon der vierte, ein langsamerer Microcode Interpreter. Au�erdem kann der

PIII nur 20 Basisbefehle zwischenspeichern. Der PIII verf�gt auch nur �ber zwei IEU

Ports, von denen einer zus�tzlich noch mit einer Menge anderer Aufgaben belastet wird.

Dort finden sich n�mlich noch die FPU Einheiten, die beim Athlon-Design abgekoppelt sind.

Damit die Einheiten der CPU m�glichst gut

parallel arbeiten, wandern die Befehle durch sogenannte Pipelines. Dabei ist vor allem die

L�nge der Pipeline wichtig, denn eine zu lange Pipeline kann bei Sprungbefehlen im

Programmecode k�nnen zu langen Wartezeiten, da die Pipline erst wieder mit neuen Befehlen

"best�ckt" werden mu�. Um dieses Problem zu umgehen mu� man also eine

m�glichst gute Sprungvorhersage treffen. Wenn man schon vorher ziemlich genau wei�, wo

es weitergeht, kann die Pipeline auch h�chstwarscheinlich richtig gef�llt werden.

Auch bei eben dieser Sprungvorhersage steckt der

Athlon den PIII in die Tasche. Er verwalten dazu n�mlich in seiner Branch Prediction

Table zwei Buffer. In dem einen Buffer werden die Zieladressen und in dem anderen das

Sprungverhalten gespeichert. Die beiden Buffer k�nnen 2048 bzw 4096 Eintr�ge speichern.

Die Vorhersageeinheit soll damit in 95% aller F�lle richtig liegen. Die Vorhersageeinheit

der PIII arbeitet lediglich mit einem 512 Eintr�ge gro�en Buffer, der die Zieladressen

verwaltet. Bedenkt man nun, da� die Pipelines beim PIII l�nger sind als die des Athlon -

also auch der Aufwand bei Fehlvorhersagen gr��er ist -, so kann man sich vorstellen,

da� der Athlon in diesem Bereich optimaler arbeitet.

Der Athlon besitzt noch keine

Prozessorseriennummer, wie sie der Intel Pentium III hat. Das hei�t aber nicht, das AMD

nicht an ein solches "Feature" gedacht hat. Um den Sicherheitsdiskussionen aus

dem Weg zu gehen, will man bei AMD folgenden Weg einschlagen: Es soll Versionen mit und

ohne Prozessorseriennummer geben, so da� sich jeder die CPU ausw�hlen kann, die er

w�nscht. Also dort, wo Sicherheit gefragt ist, mit Seriennummer und zu Hause, im privaten

Bereich, ohne. Dabei wird die Seriennummer nicht einfach ausgeschaltet, sondern sie wird

von der Hardwareseite aus nicht im Prozessor integriert.

Man sieht also recht deutlich, da� der Athlon

eine stark verbesserte und durchdachte Architektur aufweist. Es ist eben ein Prozessor

einer neuen Generation. Ein Vergleich zum PIII ist also in der Tat - wie AMD so gerne

betont - ein wenig unfair. Richtig interessant wird es also, wenn der erste Intel

Prozessor der siebten Generation an die T�r klopft.

Flexibler Cache

Vergleicht man die rein technischen Daten des

Athlon mit denen des Pentium III Prozessors, so f�llt schon als erstes auf, da� der

Athlon von seinen Erbauern mit einem gr��eren Cache gesegnet wurde. Der L1-Cache des

Athlon ist zwei mal 64 KByte gro�, was - nebenbei bemerkt - der Speicherkapazit�t von

zwei Commodore C64 entspricht :). Der L1-Cache des Pentium ist nur 1/4 so gro�, n�mlich

2 mal 16 KByte.

Beim L2 Cache findet man zur Zeit noch keine

Unterschiede. Der L2 Cache befindet sich genau wie beim PIII extern auf dem

Prozessormodul, ist 512KByte gro� und wird mit halbem Prozessortakt betrieben. AMD hat in

seiner Roadmap aber bereits einen gesockelten Athlon in Planung, der den L2 Cache (wie der

K6-III) auf dem Die (Prozessorkern) haben wird. Daf�r wird es allerdings wieder einen

neuen Sockel mit dem EV6 Busprotokol geben.

In Zukunft wird sich beim Athlon in Sachen Cache

aber einiges tun. Der Cache-Controller ist beim PIII Prozessor in einem separaten Chip auf

dem Modul untergebracht. Dies ist beim Athlon anders, hier befindet sich der

Cache-Controller mit auf dem Die. Der Controller ist zudem �u�erst anpassungsf�hig,

denn er erlaubt Taktraten von 1:1, 1:2, 2:3 und 1:3. Au�erdem kann er Cachegr��en von

512 Kbyte bis zu 8 Megabyte verwalten. Der Cache wird dabei �ber einen 72 Bit Bus

angesteuert in dem 8 Bit f�r Fehlerkorrektur benutzt werden.

Die M�glichkeit, den Prozessor mit

verschiedenen Cachegr��en und mit verschiedenen Taktraten zu best�cken wird uns in

Zukunft sicher verschiedene Athlon Modelle bescheren, die aber alle den gleichen

Prozessorkern besitzen werden. Zum einen werden das Athlon-Prozessoren mit kleinem,

schnellen Cache und zum anderen solche mit gro�em, langsameren Cache f�r den

Serverbetrieb sein. Letztere Prozessoren werden direkte Konkurrenten zu Intels Xeon

Prozessor und vermutlich auch genauso teuer sein Wahrscheinlich werden diese Prozessoren

mit kleinen Namen Add-Ons versehen. Wie w�re es zum Beispiel mit Athlon Ultra oder Athlon

Pro?

Wer hat die beste

FPU

Das schwarze Schaf bei AMD Prozessoren war

bisher immer die FPU (Floating Point Uit = Flie�kommaeinheit). W�hren die

Intergerleistung einige Male die der Intel-Prozessoren hinter sich lie�, mu�te AMD bei

der FPU immer zur�ckstecken. Auch dies hat sich nun ge�ndert. Im Athlon Prozessor

sind (wie im obigen Schema sch�n zu sehen) drei Einheiten f�r FPU, MMX oder 3DNow!

zust�ndig. Eine davon ist f�r das Abspeichern zust�ndig (FStore), die zweite erledigt

normale FPU Operationen (FADD) und die dritte ist f�r die Multiplikationen (FMUL)

zust�ndig.

Die FPU ist beim Athlon jetzt auch wie beim

PII/III "fully Pipelined", was bedeutet, da� er bereits nach einem Takt mit der

Bearbeitung des n�chsten FPU Befehls beginnen kann. Der PII Prozessor war vor allem aus

diesem Grund dem K6 III in der FPU Leistung �berlegen, denn der K6 III hat keine Pipeline

f�r den FPU Betrieb. Die bessere Leistung der FPU beim Athlon hat aber noch andere

Gr�nde. Die FPU des Athlon ist einfach leistungsf�higer, und zwar um ca. 50%. AMD

hat n�mlich schlicht und ergreifend die Rechenzeiten in der FPU optimiert.

Auch bei MMX und 3DNow! hat AMD noch einmal

in Vergleich zum K6-III zugelegt. Der Athlon hat nun denselben MMX Befehlssatz wie der

PIII besitzt, indem er mit 19 zus�tzlichen Befehlen best�ckt wurde. Aber auch die

3D-Now-Instruktionen wurden von 21 auf 26 St�ck erh�ht. Man mu� also sagen, da� AMD in

Sachen FPU m�chtig zugelegt und jetzt die Nase vorn hat. Hoffen wir, da� die Software

auch rege Gebrauch davon machen wird. Die Erweiterungen 3DNow! und ISSE sind nun in etwa

gleichwertig und, so wie es aussieht, auch genauso gut unterst�tzt.

Der Athlon unterscheidet sich aber nicht nur vom

inneren Aufbau her vom Pentium III, sondern auch in der Verbindung zur

"Au�enwelt"

Alle Mann an den Bus

Wenn man den Athlon Prozessor in der Hand h�lt

k�nnte man schnell in Versuchung kommen, diesen in ein Slot 1 Motherboard zu stecken.

Leider hat man da, wie bereits erw�hnt, keine Chance. Der von AMD verwendete Slot A ist

zwar rein mechanisch gesehen zum Slot 1 kompatibel, aber das von AMD verwendete

Busprotokoll ist grundverschieden.

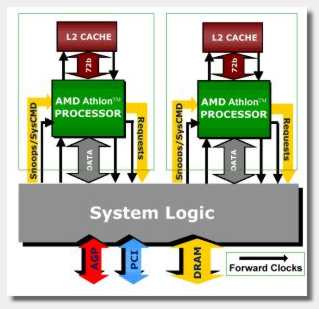

Beim Bus hat sich AMD n�mlich dazu entschlossen

das Rad nicht zweimal zu erfinden und deshalb das EV6-Busprotokol von Digital lizensiert,

das beim Alpha 21264 Prozessor eingesetzt wird. Dieser Bus arbeitet mit 100MHz auf

beiden Seiten der Taktflanke bei 64 Bit, also praktisch mit 200MHz. Damit besitzt er eine

maximale Transferrate von 1,6 GByte/s und ist damit doppelt so schnell wie der von Intel

beim Slot 1 verwendete GTL+ Bus. Bedenkt man, da� �ber diesen Bus auch DRAM (100MHz),

AGP (66MHZ) und PCI (33MHz) bedient werden und addiert diese Werte, so kommt man hier auch

auf insgesamt 200MHz (im unteren Bild sehr gut zu sehen). Der Bus k�nnte also theoretisch

alle drei Einheiten mit voller Taktrate ansteuern. Sp�ter soll dieser Bus bei AMD

�brigens auch mit 133 MHz und letztendlich sogar mit 200MHz betrieben werden (auf beiden

Seiten der Taktflanke), was vor allem bei AGP 4x zum Tragen kommen k�nnte. Damit sind

dann Transferraten von 3.2 Gbyte/s m�glich.

Der wohl gr��te Unterschied zwischen

dem EV6 und dem PIII-Busprotokol tritt beim Multiprozessorbetrieb zum Vorschein. Das EV6

Protokoll basiert n�mlich auf einer Point to Point Verbindung. Dabei verf�gt jeder

Prozessor praktisch �ber seinen eigenen Bus, er besitzt sozusagen seine "eigene

Stra�e" zum System. Der wohl gr��te Unterschied zwischen

dem EV6 und dem PIII-Busprotokol tritt beim Multiprozessorbetrieb zum Vorschein. Das EV6

Protokoll basiert n�mlich auf einer Point to Point Verbindung. Dabei verf�gt jeder

Prozessor praktisch �ber seinen eigenen Bus, er besitzt sozusagen seine "eigene

Stra�e" zum System.

Dies hat auf der einen Seite den Vorteil, da�

ein Prozessor sich die Bandbreite nicht mit den anderen Prozessoren teilen mu�, wie

das beim Penitium II/III mit zwei Prozessoren oder beim Xeon sogar mit bis zu vier St�ck

der Fall ist.

Auf der anderen Seite wird dadurch das gesamte

Boarddesign erheblich aufwendiger. Zum Gl�ck hat auch hier Digital schon einiges an

"Vorarbeit" geleistet und einen Dualprozessor Chipsatz names Tsunami entwickelt.

AMD kann also auch hier auf eine solide Gundlage zur�ckgreifen. Ein solches Board d�rfte

allerdings seinen Preis haben. Bisher gibt es noch keinen Chipsatz f�r ein vier Prozessor

System, wie es zum Beipspiel f�r den Xeon zur Verf�gung steht. Das Problem ist dabei gar

nicht die Theorie, das EV6 Busprotokol selbst kann theoretisch bis zu 14 Prozessoren

unterst�tzen, sondern die Praxis. Der Aufwand ein Athlon System mit so vielen Prozessoren

zu entwicklen ist so gro�, da� es einfach viel zu teuer w�rde. Selbst ein System mit 4

Prozessoren w�rde wahrscheinlich im Vergleich zur Leistungssteigerung deutlich zu viel

kosten.

Aber nun genug der grauen Theorie. Wie verh�lt

sich der AMD in der Praxis? Kann der Athlon seinen Technikvorsprung auch bei den

Benchmarks unter Beweis stellen?

N�chste

Seite

|

KING DEALS! Jetzt HIER bis zu 45% auf Top-Hardware von Markenherstellern sparen!

KING DEALS! Jetzt HIER bis zu 45% auf Top-Hardware von Markenherstellern sparen!  KING DEALS! Jetzt HIER bis zu 45% auf Top-Hardware von Markenherstellern sparen!

KING DEALS! Jetzt HIER bis zu 45% auf Top-Hardware von Markenherstellern sparen!